北航计组-P3课上

通过阅读本文,你可以大致了解BUAA 2024秋季 P3课上测试的相关内容

题目每年都会发生变化,题面仅靠回忆,题意描述可能与原题有一定差异

写在前面

唉唉,P3就挂了,当头一棒啊 😭 >﹏<

刚过P4课下,想着写一篇博客来记录下挂P3的感受以及一些血与泪的经验教训,希望generations to come 不要重蹈覆辙呀 😅

不过确实P3课上有一定的压力,最后延长了半小时,不过本人倒是一题没过,菜到家了😭,想看课上心路历程(第一视角破防)的直接跳转后面即可

题目

CWP

指令格式为CWP rs, rt, Imm_16

大致是说要将Imm_16符号扩展后左移两位与当前PC值进行比较,如果Imm_16大于PC,则将原来的Imm_16存到rs,否则存到rt(也可能反过来,不太记得了)

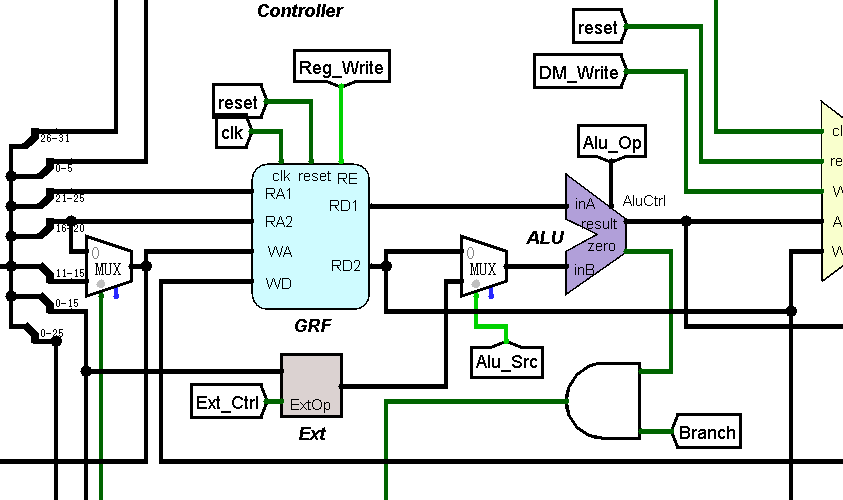

让我们来思考本题中哪些地方需要更改,首先是ALU模块的第一个输入inA前加一个多路选择器,要把PC作为输入,同时GRF模块的写入地址和写入数据均需要加一个多路选择器。因为之前课下的指令均不涉及对rs寄存器的写入,所以写入地址前得加。整体思路没什么困难,但是如果你之前没有预留接口,以及Logiism电路很紧凑的话,你可能会改的比较吃力,别问我怎么知道的 QAQ

至于判断条件的话,可以在ALU里实现并且沿用之前beq的zero端口,当然对于本指令,需要在Controller模块新加一个输出信号。

BGC

指令格式为BGC rs, rt, Imm_16

大致是说将GR[rs]和GRF[rt] 32位的每两位转换为对应的格雷码,并比较二者转换后的32位数中 1 的个数,如果一个大于另一个,则按照offset_16跳转

格雷码转换:00-00 01-01 10-11 11-10

如果没什么思路可以设计一个2bit的格雷码转换程序,再暴力解决,最后别忘了bit adder这个元件,可以直接统计其中1的个数

当然,可以发现,格雷码转换其实就是:逻辑右移一位再与原数异或,其实直接真值表打表也挺容易

复用beq的跳转即可,注意对跳转信号的判断

LWSO

比较复杂,我课上没想,,请移步其他大佬的博客 (❁´◡`❁)

总结

针对我课上出的问题以及课下来发现的问题及反思,总结了几点供后来的学弟学妹借鉴,希望你们不要重蹈覆辙了😎

- 课下充分测试,与同学对拍,保证不留bug

- 预留接口给新的指令和新的信号,比如直接添加一个New信号在课下的Controller里面,但先不连接

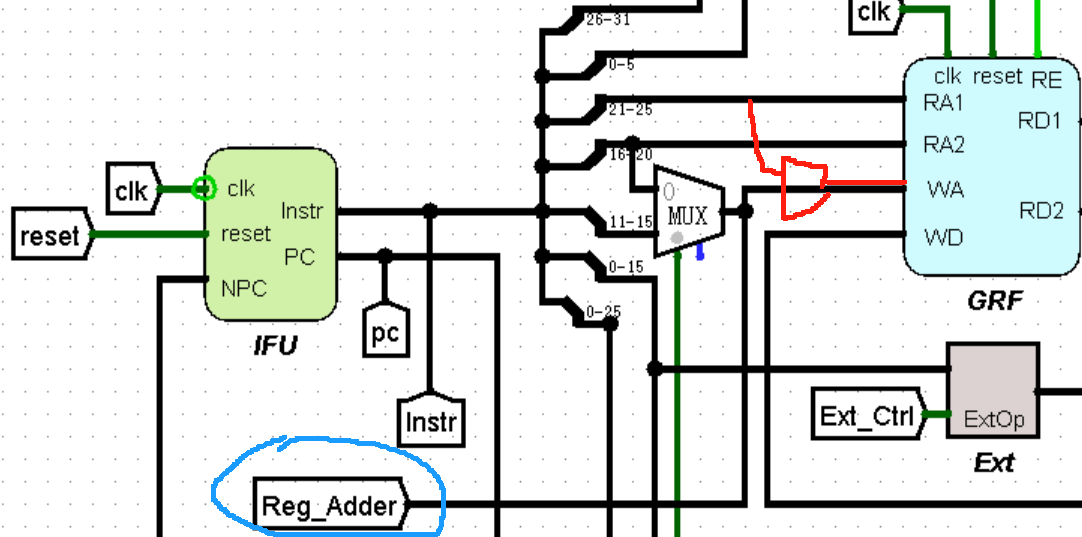

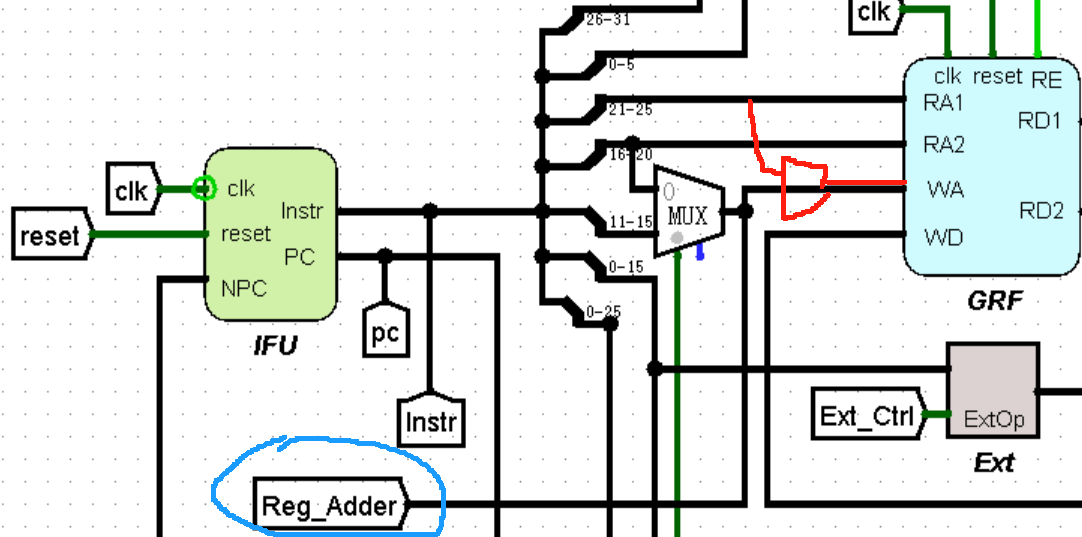

- 模块间,端口处,留出适当的距离,不要像我一样加MUX时手忙脚乱,一个反面例子如下:

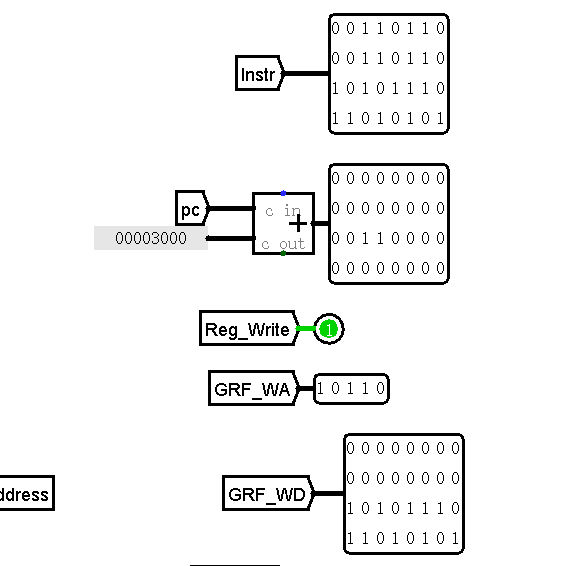

- 课程组要求输出的那些个信号对应的Tunnel,一定要检查是否是最终的正确信号,不要在Tunnel和端口间更改信号,这样会导致本地运行正确但输出错误,很难debug,因为课程组为了评测,会让你把相关信号输出出去,像这样:

- 如果你像上面说的那样做了,会出问题,具体情况见我的心路历程-第二天部分debug发现的毛病,后来发现不少同学都有这个问题,希望后来人能够引以为戒,这都是学长学姐亲自踩的坑啊 ε=(´ο`*)))唉

反面教材如下:

最后,如果你对我出的bug感兴趣并且想知道我课上有多难受的话,请接着往下看

心路历程

课上

你能知道我T1调了半天,本地各种测试各种没问题,加上去死活不对的感受嘛😭麻烦的是,评测机并不会在出错的地方立马报错,而是会在后面几条指令的某一条报错,而我的则是一条lw指令。当时翻译出来人都蒙了,我课下测试了那么多数据,怎么能有问题呢?而且我裸交一发对了2个点,没问题呀,于是我返回去检查课上的通路,一通测试下来,找不出任何问题,各种数据都测完了,我已经筋疲力竭了,此时已快到8点,而我第一题还没过,,看看周围的同学,我知道,这次有点悬;于是我检查课下去了,检查一番又检查测试课上,在这样的反复中迷失了自我,又过了15min,这下我彻底慌神了,本地测试没有问题啊,交上去就是不对,能有什么办法呢?不知道有没有人能感受到我的绝望≡(▔﹏▔)≡

于是,我诚惶诚恐地打开了第二题,一看感觉直接将32位每两位转换为格雷码,好麻烦,也不想新建模块,于是开始冥思苦想,试图打开什么新思路,期间还瞄了一眼第三题,感觉很复杂,一看就不想做。

终于到了8点半,一事无成的我决定开始摆烂,思考人生,我趴在桌上,脑子想的什么呢?🤔是从Pre以来的披荆斩棘吗?是P3课下测试对拍的欢乐吗?是校庆时在摊位上玩游戏的激情吗?还是来6系充实繁忙的每一天呢?我不知道,我的脑子一片空白。期间还看到zlr助教gg看了一眼我,又看了一眼平板,不知道他又对我有何感想呢?

时间很快来到了8.58,我一看,大部分人跟我一样,被硬控在了新北地下的机房里,只有少数寥寥的几个座位是空的,说实话,我的心里竟然感到一丝慰藉,还有这么多人也没过啊(buhsi)

但是,考试延迟了半小时,期间有一部分人做出来了走了,也有一些人像我一样留到了最后,九点半走出机房,看到同行的人也是垂头丧气,大家心里都很不是滋味🙃

第二天

回到寝室后,我望着课下的电路,脑子里一片茫然,一种无力感裹挟着我,让我说不出话来,期间看了紫玉哥哥的题解,也看了水群里大伙的讨论,还找亲爱的助教zjygg倾诉了一番,但心里依旧难过。

上床后,很快睡着了,第二天物理课,我和vach(室友)坐在一起,谈论着P3,才发现他也没过,偷笑

🤓 ,我打开P3课下,准备重构一番,毕竟课上加通路加的难受,就在我给GRF的写入地址加一个标签的时候,我猛地意识到了自己的课上bug,见下图

我课上是直接把多路选择器加在了红色位置,但是我的寄存器写入地址的Tunnel还是接在了原来的蓝色位置,也就导致了输出地址的问题。更恐怖的是,我课上debug是直接接了probe在GRF的WA前面,完全没有管Reg_Addr的输出问题,这也是我本地测试毫无问题,交上去报错奇奇怪怪的原因,哎😱

到这里,我真想穿越回去课上改掉这个bug,但时间无法倒流,哎。那个时刻,我真正知道了什么叫欲哭无泪

中午去给空天杯篮球赛当志愿者,记分员,沉浸在了比赛里,忘掉了昨晚的悲痛,也感谢这个志愿活动,让我成功走了出来,忘掉烦恼,笑对生活😄